## Lecture Notes in Computer Science

1575

Edited by G. Goos, J. Hartmanis and J. van Leeuwen

# Springer

Berlin

Heidelberg

New York

Barcelona

Hong Kong

London

Milan

Paris

Singapore

Tokyo

# Compiler Construction

8th International Conference, CC'99

Held as Part of the Joint European Conferences

on Theory and Practice of Software, ETAPS'99

Amsterdam, The Netherlands, March 22-28, 1999

Proceedings

#### Series Editors

Gerhard Goos, Karlsruhe University, Germany Juris Hartmanis, Cornell University, NY, USA Jan van Leeuwen, Utrecht University, The Netherlands

Volume Editor

Stefan Jähnichen Technische Universität Berlin, Fachbereich 13 - Informatik Sekretariat SWT FR 5-6 Franklinstr. 28-29, D-10587 Berlin, Germany E-mail: jaehn@cs.tu-berlin.de

Cataloging-in-Publication data applied for

#### Die Deutsche Bibliothek - CIP-Einheitsaufnahme

Compiler construction: 8th international conference; proceedings / CC '99, held as part of the Joint European Conferences on Theory and Practice of Software, ETAPS '99, Amsterdam, The Netherlands, March 22 - 28, 1999. Stefan Jähnichen (ed.). - Berlin; Heidelberg; New York; Barcelona; Hong Kong; London; Milan; Paris; Singapore; Tokyo: Springer, 1999

(Lecture notes in computer science; Vol. 1575)

ISBN 3-540-65717-7

CR Subject Classification (1998): D.3.4, D.3.1, F.4.2, D.2.6, I.2.2 ISSN 0302-9743 ISBN 3-540-65717-7 Springer-Verlag Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer-Verlag. Violations are liable for prosecution under the German Copyright Law.

© Springer-Verlag Berlin Heidelberg 1999 Printed in Germany

Typesetting: Camera-ready by author SPIN 10703066 06/3142 - 5 4 3 2 1 0 Printed on acid-free paper

## Foreword

ETAPS'99 is the second instance of the European Joint Conferences on Theory and Practice of Software. ETAPS is an annual federated conference that was established in 1998 by combining a number of existing and new conferences. This year it comprises five conferences (FOSSACS, FASE, ESOP, CC, TACAS), four satellite workshops (CMCS, AS, WAGA, CoFI), seven invited lectures, two invited tutorials, and six contributed tutorials.

The events that comprise ETAPS address various aspects of the system development process, including specification, design, implementation, analysis and improvement. The languages, methodologies and tools which support these activities are all well within its scope. Different blends of theory and practice are represented, with an inclination towards theory with a practical motivation on one hand and soundly-based practice on the other. Many of the issues involved in software design apply to systems in general, including hardware systems, and the emphasis on software is not intended to be exclusive.

ETAPS is a loose confederation in which each event retains its own identity, with a separate programme committee and independent proceedings. Its format is open-ended, allowing it to grow and evolve as time goes by. Contributed talks and system demonstrations are in synchronized parallel sessions, with invited lectures in plenary sessions. Two of the invited lectures are reserved for "unifying" talks on topics of interest to the whole range of ETAPS attendees. As an experiment, ETAPS'99 also includes two invited tutorials on topics of special interest. The aim of cramming all this activity into a single one-week meeting is to create a strong magnet for academic and industrial researchers working on topics within its scope, giving them the opportunity to learn about research in related areas, and thereby to foster new and existing links between work in areas that have hitherto been addressed in separate meetings.

ETAPS'99 has been organized by Jan Bergstra of CWI and the University of Amsterdam together with Frans Snijders of CWI. Overall planning for ETAPS'99 was the responsibility of the ETAPS Steering Committee, whose current membership is:

André Arnold (Bordeaux), Egidio Astesiano (Genoa), Jan Bergstra (Amsterdam), Ed Brinksma (Enschede), Rance Cleaveland (Stony Brook), Pierpaolo Degano (Pisa), Hartmut Ehrig (Berlin), José Fiadeiro (Lisbon), Jean-Pierre Finance (Nancy), Marie-Claude Gaudel (Paris), Susanne Graf (Grenoble), Stefan Jähnichen (Berlin), Paul Klint (Amsterdam), Kai Koskimies (Tampere), Tom Maibaum (London), Ugo Montanari (Pisa), Hanne Riis Nielson (Aarhus), Fernando Orejas (Barcelona), Don Sannella (Edinburgh), Gert Smolka (Saarbrücken), Doaitse Swierstra (Utrecht), Wolfgang Thomas (Aachen), Jerzy Tiuryn (Warsaw), David Watt (Glasgow)

ETAPS'98 has received generous sponsorship from:

- KPN Research

- Philips Research

- The EU programme "Training and Mobility of Researchers"

- CWI

- The University of Amsterdam

- The European Association for Programming Languages and Systems

- The European Association for Theoretical Computer Science

I would like to express my sincere gratitude to all of these people and organizations, the programme committee members of the ETAPS conferences, the organizers of the satellite events, the speakers themselves, and finally Springer-Verlag for agreeing to publish the ETAPS proceedings.

Edinburgh, January 1999 Donald Sannella

ETAPS Steering Committee Chairman

## **Preface**

The present proceedings of the 1999 Compiler Construction Conference are, quite apart from the highly topical nature of the subjects addressed, remarkable for two reasons. First, I feel they illustrate very well the fact that this is still one of the most interesting research areas in computer science, and that it is possible to push the boundaries of knowledge here even further, thanks in large part to the growing theoretical penetration of the subject-matter. Second, both the quantity and quality of the contributions are a clear indication that the Compiler Compiler Conference has become firmly established not only as a part of ETAPS, but in its own right and with its own "regular" and highly motivated group of participants.

The number of papers submitted has remained roughly the same compared with previous years, as has the number of papers selected for presentation. Although, to begin with, I had – in my capacity as Program Committee Chair – favored a physical meeting of PC members and had practically called for such a meeting in my letter of invitation, I soon decided to first wait and see how the selection process and electronic discussion went – with the result that we were, ultimately, able to dispense with the meeting.

This proved possible thanks not only to the use of an electronic conference system, provided courtesy of Vladimiro Sassone, but also and in particular to Jochen Burghardt's willingness to assist me in the PC work and to take full charge of technical support for the installation and use of the relevant software. And I think all PC members will join me in saying he did a great job and is owed our thanks for ensuring that the submission, selection and publication procedures went so smoothly.

I am also indebted, though, to my colleagues in the Program Committee for their willingness to cooperate so closely in these procedures and to offer their technical expertise in the refereeing and discussion process, thus making a major contribution to the successful production of the present volume. My thanks also go to Don Sanella, who was in charge of the ETAPS organization, for his many practical suggestions on how to improve procedures and for his strict but necessary demands that deadlines be met.

Last but not least, I wish to thank all those who submitted papers for the conference. Even if your paper was not accepted this time, I would like to express my appreciation for the time and effort you invested and hope to be able to welcome you to the conference in Amsterdam all the same.

Finally, a last word of thanks to the team at Springer-Verlag for their excellent work and cooperation in preparing the present volume. I hope you will all enjoy reading it!

Berlin, January 1999

Stefan Jähnichen CC Program Committee Chairman

## **Program Committee**

Rudolf Eigenmann (USA), Guang R. Gao (USA), Francois Irigoin (France), Stefan Jähnichen (Chair, Germany), Thomas Johnsson (Sweden), Derrick Kourie (South Africa), Olivier Michel (France), Jerzy Nawrocki (Poland), Lawrence Rauchwerger (USA), Yves Robert (France), Mooly Sagiv (Israel), Martin Simons (Germany), Chau-Wen Tseng (USA), David A. Watt (Scotland), Reinhard Wilhelm (Germany), Hans Zima (Austria)

## Referees

| V. Adve        | C. Dubois      | M. Langenbach   | S. Rubin         |

|----------------|----------------|-----------------|------------------|

| G. Agrawal     | C. Eisenbeis   | E. Laure        | H. Saito         |

| M. Aiguier     | A. Engelbrecht | D. Lavery       | D. Sehr          |

| N. Aizikowitz  | T. Fahringer   | Y. Lee          | H. Seidl         |

| J. Amaral      | C. Ferdinand   | A. Marquez      | G. Silber        |

| R. Amir        | A. Fraboulet   | L. Marshall     | V. Sipkova       |

| J. Bechennec   | T. Geiger      | E. Mehofer      | A. Stoutchinin   |

| B. Blount      | J. Giavitto    | J. Merlin       | B. Su            |

| W. Blume       | M. Gupta       | A. Mignotte     | X. Tang          |

| R. Bodik       | M. Hall        | P. Moreau       | S. Thesing       |

| P. Brezany     | P. Havlak      | J. O'Donnell    | D. Xinmin Tian   |

| J. Burghardt   | R. Heckmann    | Y. Paek         | P. Tu            |

| F. Cappello    | J. Hoeflinger  | I. Park         | T. Vijaykumar    |

| M. Chakarvarty | G. Huard       | W. Pfannenstiel | M. Voss          |

| S. Chatterjee  | D. Kaestner    | A. Pierantonio  | J. Wang          |

| W. Complak     | R. Kennell     | S. Pinter       | B. Watson        |

| Q. Cutts       | S. Wook Kim    | J. Prins        | B. Wender        |

| A. Czajka      | J. Knoop       | C. Probst       | A. Wojciechowski |

| F. Delaplace   | U. Kremer      | F. Rastello     | A. Zaks          |

| J. Delosme     | P. W. Kutter   | N. Ros          | C. Zhang         |

| S. Diehl       | A. Lallouet    | J. Ross         | W. Zhao          |

|                |                |                 |                  |

## **Table of Contents**

| Compiler Generation                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| Data Structure Free Compilation                                                                                                         |

| Debugging Eli-Generated Compilers with Noosa                                                                                            |

| Faster Generalized LR Parsing                                                                                                           |

| Interprocedural Analysis                                                                                                                |

| Interprocedural Path Profiling                                                                                                          |

| Experimental Comparison of call string and functional Approaches to Interprocedural Analysis                                            |

| Link-Time Improvement of Scheme Programs                                                                                                |

| Code Optimization                                                                                                                       |

| Expansion-Based Removal of Semantic Partial Redundancies                                                                                |

| Register Pressure Sensitive Redundancy Elimination                                                                                      |

| Code Optimization by Integer Linear Programming                                                                                         |

| Evaluation of Algorithms for Local Register Allocation                                                                                  |

| Parallelization Techniques                                                                                                              |

| Efficient State-Diagram Construction Methods for Software Pipelining 153 Chihong Zhang, Ramaswamy Govindarajan, Sean Ryan, Guang R. Gao |

| A Comparison of Compiler Tiling Algorithms                                                                                              |

| Implementation Issues of Loop-Level Speculative                                                                         | 100 |

|-------------------------------------------------------------------------------------------------------------------------|-----|

| Run-Time Parallelization                                                                                                | 183 |

| Dawrence Rauchwerger, Devang I wei                                                                                      |     |

| Compiler Systems                                                                                                        |     |

| Compilation and Memory Management for ASF+SDF                                                                           | 198 |

| The Design of the PROMIS Compiler                                                                                       | 214 |

| Program Transformation                                                                                                  |     |

| Floating Point to Fixed Point Conversion of C Code                                                                      | 229 |

| Optimizing Object-Oriented Languages Through<br>Architectural Transformations                                           | 244 |

| Cache Specific Optimization                                                                                             |     |

| Virtual Cache Line: A New Technique to Improve<br>Cache Exploitation for Recursive Data Structures                      | 259 |

| Extending Modulo Scheduling with Memory Reference Merging  Benoît Dupont de Dinechin                                    | 274 |

| Tool Demonstrations                                                                                                     |     |

| TRAPping Modelica with Python                                                                                           | 288 |

| A Programmable ANSI C Code Transformation Engine                                                                        | 292 |

| Tool Support for Language Design and Prototyping with Montages Matthias Anlauff, Philipp W. Kutter, Alfonso Pierantonio | 296 |

| Author Index                                                                                                            | 301 |

## **Data Structure Free Compilation**

João Saraiva<sup>1,2</sup> and Doaitse Swierstra<sup>1</sup>

Department of Computer Science

University of Utrecht, The Netherlands

Department of Computer Science

University of Minho, Braga, Portugal

{saraiva, swierstra}@cs.uu.nl

Abstract. This paper presents a technique to construct compilers expressed in a strict, purely functional setting. The compilers do not rely on any explicit data structures, like trees, stacks or queues, to efficiently perform the compilation task. They are constructed as a set of functions which are directly called by the parser. An abstract syntax tree is neither constructed nor traversed. Such deforestated compilers are automatically derived from an attribute grammar specification. Furthermore this technique can be used to efficiently implement any multiple traversal algorithm.

## 1 Introduction

Traditionally, compilers are organized in two main phases: the parsing phase and the attribute evaluation phase, with an abstract syntax tree as the intermediate data structure. The parser constructs the abstract syntax tree and the attribute evaluator decorates that tree, i.e., it computes attribute values associated to the nodes of the tree. In most implementations the attribute evaluator walks up and down in the tree, while in the mean time decorating it with attribute values. The abstract syntax tree guides the evaluator and stores attributes that are needed on different traversals of the compiler.

This paper presents a new technique for constructing compilers as a set of strict, side-effect free functions. Furthermore the compilers are completely *deforestated*, *i.e.*, no explicit intermediate data structure (*e.g.*, abstract syntax tree) has to be defined, constructed, nor traversed. The parser directly calls attribute evaluation functions, the so-called *visit-functions*. Moreover all the attributes are handled in a canonical way: they just show up as arguments and results of visit-functions.

Because our attribute evaluators are independent of any particular data structure definition, they are more generic than classical attribute evaluators. They are highly reusable and new semantics can easily be added to the attribute evaluators, even when separate analysis of compiler components is considered. For example, new productions can be incorporated to an existent compiler without changing its attribute evaluator. The visit-functions which implement the new productions are simply added to the compiler.

Although it is possible to apply these techniques in hand-written compilers, it is much easier to generate them from an *Attribute Grammar* [Knu68]. Our techniques were developed in the context of the incremental evaluation of (Higher-order) attribute grammars: efficient incremental behaviour is achieved by memoization of visit-function calls [PSV92].

In Section 2 we briefly introduce attribute grammars, present a simple attribute grammar and describe attribute evaluators based on the visit-sequence paradigm. In Section 3  $\lambda$ -attribute evaluators are introduced. Section 4 deals with parse-time attribute evaluation. Section 5 discusses other applications of our techniques and section 6 briefly discusses the current implementation. Section 7 contains the conclusions.

## 2 Attribute Grammars

The compilers considered in this paper are specified through an Attribute Grammar (AG) [Knu68] which belong to the class of Ordered Attribute Grammars [Kas80]. These AGs have proven to be a suitable formalism for describing programming languages and their associated tools, like compilers, language based editors, etc. From an AG a parser and an Attribute Evaluator (AE) can automatically be derived.

This section introduces an attribute grammar which acts as the running example throughout this paper. Using it, we present the concept of visit-sequences [Kas80] which are the basis of our techniques.

## 2.1 The Block Language Example

This section presents a analyser for an extremely small language, called BLOCK, which deals with the *scope* of variables in a *block structured language*. An example BLOCK program is:

This language does not require that declarations of identifiers occur before their first use. Furthermore an identifier from a global scope is visible in a local scope only if is not hidden by an a declarations with a same identifier in a more local scope. In a block an identifier may be declared at most once. The above program contains two errors: at the outer level the variable x has been declared twice and the use of the variable w has no binding occurrence at all.

Because we allow a *use-before-declare* discipline, a conventional implementation of the required analysis naturally leads to a program that traverses each block twice: once for processing the declarations of identifiers and constructing

an environment and once for processing the uses of identifiers using the computed environment to check for the use of non-declared names. The uniqueness of names is checked in the first traversal: for each newly encountered declaration it is checked whether that identifier has already been declared in this block. In that case an error message is computed. Since we need to distinguish between identifiers declared at different levels, we introduce an inherited attribute lev indicating the nesting level of a block. The environment is a list of bindings of the form (name, lev).

In order to make the problem more interesting, and to demonstrate our techniques, we require that the error messages produced in both traversals are to be merged in order to generate a list of errors which follows the sequential structure of the program.

Figure 1 presents the attribute grammar defining the BLOCK language. We use a standard AG notation: Productions are labelled with a name for future references. Within the attribution rules of a production, different occurrences of the same symbol are denoted by distinct subscripts. Inherited (synthesized) attributes are denoted with the down (up) arrow  $\downarrow$  ( $\uparrow$ ). As usual in AGs we distinguish two classes of terminals: the  $literal\ symbols\ (e.g.,\ ':',\ 'decl',\ etc)$  which do not play a role in the attribution rules and the  $pseudo\ terminal\ symbols\ (e.g.,\ name)$ , which are non-terminal symbols for which the productions are implicit (traditionally provided by an external lexical analyser). Pseudo terminal symbols are syntactically referenced in the AG, i.e., they are used directly as values in the attribution rules. The attribution rules are written as Haskell-like expressions. The semantic functions mustbein and mustnotbein define usual symbol table lookup operations.

```

root Proq

Proa

<\uparrow errors>

Prog \rightarrow \text{ROOTP} (Its)

\langle | lev, | dcli, | env, | dclo, | errors \rangle

Its.lev

= 0

It \rightarrow \text{USE} ('use' name)

Its.dcli

= []

It.dclo

= It.dcli

Its.env

= Its.dclo

It.errors = name 'mustbein' It.env

Prog.errors = Its.errors

| DECL ('dcl' name)

= (name It.lev)

It.dclo

<\downarrow lev, \downarrow dcli, \downarrow env, \uparrow dclo, \uparrow errors >

: It.dcli

Its \rightarrow Nillits ()

= (name It.lev)

It.errors

Its.dclo

= Its.dcli

`mustnotbein` It.dcli

Its.errors = []

| BLOCK ('blk', '(', Its')')

Consits (It; Its)

Its.lev = It.lev + 1

It.lev

= Its_1.lev

Its.dcli = It.env

Its_2.lev

= Its_1.lev

Its.env = Its.dclo

It.dcli

= Its_1.dcli

It.dclo = It.dcli

Its_2.dcli

= It.dclo

It.error = Its.errors

It.env

= Its_1.env

Its_2.env

= Its_1.env

Its_1.errors = It.errors + + Its_2.errors

```

Fig. 1. The Block Attribute Grammar.

## 2.2 Structured Visit-Sequences

The attribute evaluators considered in this paper are based on the visit-sequence paradigm [Kas80].

A visit-sequence describes, for a node in the tree, the sequence of states the node will go through when the abstract syntax tree is decorated. The essential property is that this sequence depends solely on the production at the node, and not on the context in which it occurs, hence we denote vis(p) to denote the visit-sequence associated to production p. In a visit-sequence evaluator, the number of visits to a non-terminal is fixed, and independent of the production. We denote the number of visits of non-terminal X by v(X). Each visit i to a node labelled with a production for a non-terminal X has a fixed interface. This interface consists of a set of inherited attributes of X that are available to visit i and another set of synthesized attributes that are guaranteed to be computed by visit i. We denote these two sets by  $A_{inh}(X,i)$  and  $A_{syn}(X,i)$ , respectively.

Visit-sequences are the outcome of attribute evaluation scheduling algorithms. They can be directly used to guide the decoration of a classical attribute evaluator [Kas91]. Visit-sequences, however, are the input of our generating process. It is then convenient to use a more structured representation of the visit-sequences. Thus, they are divided into visit-sub-sequences vss(p,i), containing the instructions to be performed on visit i to the production p.

In order to simplify the presentation of our algorithm, visit-sub-sequences are annotated with define and usage attribute directives. Every visit-sub-sequence vss(p,i) is annotated with the interface of visit i to X:  $inh(\alpha)$  and  $syn(\beta)$ , where  $\alpha$  ( $\beta$ ) is the list of the elements of  $A_{inh}(X,i)$  ( $A_{syn}(X,i)$ ). Every instruction eval(a) is annotated with the directive uses(bs) which specifies the attribute occurrences used to evaluate a, i.e., the occurrences that a depends on. The instruction visit(c,i) causes child c of production p to be visited for the ith time. We denote child c of p by  $p_c$  and the father (i.e. the left-hand side symbol of p) by  $p_0$ . The visit uses the attribute occurrences of  $A_{syn}(p_c,i)$ . Thus visit(c,i) is annotated with inp(is) and out(os) where is (os) is the list of the elements of  $A_{inh}(p_c,i)$  ( $A_{syn}(p_c,i)$ ).

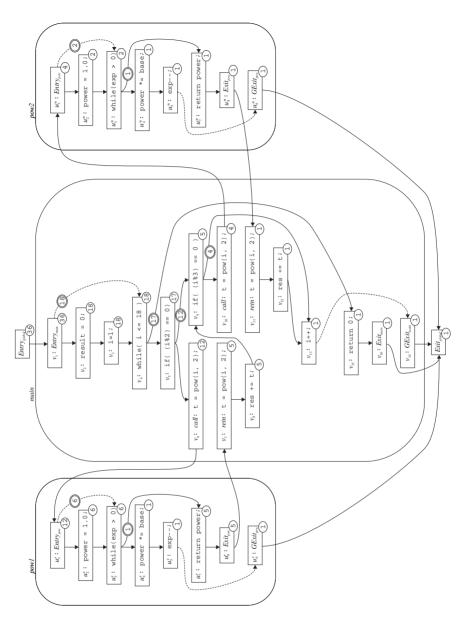

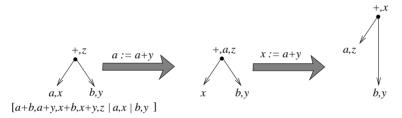

Figure 2 presents the structured and annotated visit-sub-sequences<sup>1</sup> for the productions ROOTP and BLOCK.

The visit-sequences were obtained using the Chained Scheduling Algorithm [Pen94]. Chained scheduling is a variant of Kastens' Ordered Scheduling Algorithm [Kas80]. It was designed with the aim at minimizing the number of attributes that must be passed between traversals and, in this way, improving the behaviour of functional attribute evaluators. Chained scheduling chooses the attribute evaluation order such that every attribute is computed as early as possible. The visit-sequences of figure 2 are similar to the ones produced by Kastens' algorithm. The only exception is the schedule of the instructions eval(Its.lev). Kastens' algorithm schedules this instruction to the second visit-sub-sequence of production Block. In that case, the occurrence It.lev must be retained for the second sub-sequence. A detailed analysis of both scheduling algorithms can be found in [Pen94] (chapter 5).

```

plan Block

begin 1 \text{ inh}(It.lev, It.dcli)

eval

( Its.lev )

plan ROOTP

uses(It.lev).

begin 1 inh(),

(Its.lev)

(It.dclo)

eval

eval

uses(),

uses(It.dcli)

syn(It.dclo)

(Its.dcli)

end 1

eval

uses(),

begin 2 inh(It.env)

visit (Its, 1)

eval

(Its.dcli)

inp(Its.lev, Its.dcli)

uses(It.env),

out(Its.dclo),

visit

(Its,1)

eval

(Its.env)

inp(Its.dcli, Its.lev)

uses(Its.dclo),

out(Its.dclo),

visit (Its, 2)

(Its.env)

eval

inp(Its.env)

uses(Its.dclo),

out(Its.errors),

visit

(Its,2)

(Prog.errors)

eval

inp(Its.env)

uses(Its.errors)

out(Its.errors),

syn(Prog.errors)

end 1

eval

(It.errors)

uses(Its.errors)

end 2

syn(It.errors)

```

**Fig. 2.** Structured Visit-Sequences: the attribute occurrence *Its.lev* is defined in the first traversal of Block and is used in the next one.

## 3 Deriving $\lambda$ -Attribute Evaluators

This section shows how to derive purely functional and strict attribute evaluators, starting from an available set of visit-sequences. The derived attribute evaluators are presented in Haskell. We use Haskell because it is a compact, well-defined and executable representation for our  $\lambda$ -attribute evaluators. We start by describing our techniques informally and by analysing a simple example. After that, we present the formal derivation of  $\lambda$ -attribute evaluators and we derive the evaluator for the Block language.

The  $\lambda$ -attribute evaluators consist of a set of partial parameterized visit-functions, each performing the computations of one traversal of the evaluator. Those functions return, as one of their results, the visit-functions for the next traversal. Performing the visit corresponds to totally parameterising the visit-functions and, once again returning the function for the next traversal. The main idea is that for each visit-sub-sequence we construct a function that, besides mapping inherited to synthesized attributes, also returns the function that represents the next visit. Any state information needed in future visits is passed on by partially parameterising a more general function. The only exception is the final visit-function which returns synthesized attributes.

Consider the following simplified visit-sub-sequences for production  $X \to \text{PROD}(Y \mid Z)$  (the annotations inp and out of the visit instructions are omitted since they are not relevant for this example):

```

plan Prod

begin 1 inh(X.inh_1)

visit(Y,1)

begin 2 inh(X.inh_2)

eval ···

visit (Z,1)

uses(X.inh_1,\cdots),

eval (X.syn_2)

visit(Y, 2)

uses(X.inh_1, \cdots)

eval (X.syn_1)

syn(X.syn_2)

end 2

uses(\cdots),

end 1

syn(X.syn_1)

```

Observe that, the inherited attribute  $X.inh_1$  must be explicitly passed from the first visit of X (where it is defined) to the second one (where it is used). The non-terminal Y is visited twice in the first visit to X. These two visit-sub-sequences above are implemented by the following two visit-functions:

The visit-functions  $\lambda_{Y^1}$  and  $\lambda_{Z^1}$  define the computations of the first traversal of non-terminal symbols Y and Z. The attribute occurrence X.x is passed from the first to the second traversal as a hidden result of  $\lambda_{Prod^1}$  in the form of an extra argument to  $\lambda_{Prod^2}$ . Note that **no** reference to visits for non-terminal symbol Y is included in  $\lambda_{Prod^2}$  since all the visits to Y occur in the first visit to Y. Observe also that the function  $\lambda_{Z^1}$  is directly passed to the second visit to X, where the first visit to Z is performed.

The  $\lambda$ -attribute evaluators can be automatically derived from the visit-sub-sequences, by performing an *attribute lifetime analysis*: for each attribute occurrence it is known in which visit it is *defined* and in which visit(s) it is *used*. Thus, let us introduce two predicates def and use. The predicate def(p, a, v) denotes whether attribute a of production p is defined in visit v. Likewise, use(p, a, v) denotes whether attribute a of production p is used in visit v:

```

\begin{split} \operatorname{def}(p,a,v) &= \operatorname{eval}(a) \in vss(p,v) \vee \operatorname{inh}(\dots,a,\dots) \in vss(p,v) \\ &\vee \operatorname{out}(\dots,a,\dots) \in vss(p,v) \\ \operatorname{use}(p,a,v) &= \operatorname{uses}(\dots,a,\dots) \in vss(p,v) \vee \operatorname{syn}(\dots,a,\dots) \in vss(p,v) \\ &\vee \operatorname{inp}(\dots,a,\dots) \ \in \ vss(p,v) \end{split}

```

Pseudo terminal symbols may also be used as normal attribute occurrences within the attribute equations of the AG (like the symbol name of the BLOCK AG). Consequently, we need to perform a lifetime analysis of those symbols too. Thus, we extend the above predicates to work on terminal symbols too. The terminal symbols, denoted by  $\Sigma$ , are not defined in the attribute equations, but at parse-time. So, we assign visit number 0 to the parser. The predicate def is extended as follows:

$$def(p, a, 0) = a \in \Sigma$$

An attribute or pseudo terminal symbol of a production p is alive at visit i, if it is defined in a previous visit and it is used in visit i or later. For each production p and for each of its visits i, with  $1 \le i \le v(p_0)$ , we define the set alive(p, i) which contains the live occurrences on visit i. It is defined as follows:

$$alive(p,i) = \{ a \mid \mathtt{def}(p,a,k) \ \land \ \mathtt{use}(p,a,j) \ \land \ k < i \leq j \}$$

Let us concentrate now on the analysis of the visits to the non-terminal symbols of the grammar. Let  $alive\_visits(p, c, v)$  denote the list of visits to child c of production p, which have to be performed in visit-sub-sequence v to p or in later ones. This list is defined as follows:

$$alive\_visits(p, c, v) = [$$

$visit(c, i) | visit(c, i) \in vss(p, j) , v \le j \le v(p_0)]$

Consider the visit-sub-sequences of production PROD. For the first sub-sequence we have the following visits:  $alive\_visits(PROD, 1, 1) = [visit(p_1, 1), visit(p_1, 2)]$  and  $alive\_visits(PROD, 2, 1) = [visit(p_2, 1)]$ . That is, in the first visit to PROD or later ones the non-terminal symbol Y is visited twice and the symbol Z is visited once. Note that according to the visit-sub-sequences the single visit to Z is performed in the second visit of PROD. Consider now the visit-function  $\lambda_{Prod^1}$ . Observe that its arguments contain the reference to the first traversal of Y only (argument  $\lambda_{Y^1}$ ). The function for the second traversal is obtained as a result of  $\lambda_{Y^1}$ . Observe also that the reference to the visit to Z is passed on to the second traversal of PROD, where it is called. That is, the arguments of the visit-function contain a reference to the earliest visit (function) which has to be performed for all alive non-terminal symbols.

In order to derive our visit-functions we need references (the visits-functions) to the earliest visit-function: all following references are returned by evaluating the previous ones. Thus, we define the function inspect(p,v) which takes the head of the list returned by  $nt\_vis$  (i.e., the following visit), for all non-terminal symbols of production p. This is a partial function, since the list returned by  $nt\_vis$  may be empty. This occurs when no further visits to a non-terminal symbol are performed. This function is defined as follows:

$$inspect(p, v) = \{ hd \ alive\_visits(p, c, v) : alive\_visits(p, c, v) \neq [] \land p_c \in N \}$$

where hd is the usual operation that returns the head of a list and N denotes the set of non-terminal symbols.

We describe now the derivation of the  $\lambda$ -attribute evaluator. For each production p and for each traversal i of non-terminal symbol  $p_0$  a visit-function  $\lambda_{p^i}$  is derived. The arguments of this visit-function are:

- 1. The attribute occurrences which are alive at visit i, alive(p, i),

- 2. The deforestated visit-functions derived for the right-hand side symbols of p which are inspected in traversal i or later, inspect(p, i), and

- 3. The inherited attributes of traversal i, i.e.,  $A_{inh}(p_0, i)$ .

The result is a tuple of which the first element is the partial parameterized function for the next traversal and the other elements are the synthesized attributes, *i.e.*,  $A_{syn}(p_0, i)$ . Thus, the visit-functions have the following signature:

$$\begin{array}{c} \lambda_{p^i} :: \mathit{jtype\_pp\_args}(p,i)_{\dot{\mathcal{E}}} \ \mathcal{T}(\mathit{inh\_1}) \to \cdots \to \mathcal{T}(\mathit{inh\_k}) \to \\ (\mathcal{T}(\lambda_{p^{i+1}}), \mathcal{T}(\mathit{syn\_1}), \ldots, \mathcal{T}(\mathit{syn\_l})) \end{array}$$

with  $\{inh\_1, \ldots, inh\_k\} = A_{inh}(p_0, i)$ ,  $\{syn\_1, \ldots, syn\_l\} = A_{syn}(p_0, i)$ .  $\mathcal{T}(a)$  should be interpreted as the derived type for element a. The fragment  $mat < type\_pp\_args(p, i)$ ; denotes the type of the elements in alive(p, i) and in inspect(p, i). This fragment is defined as follows:

$$[type\_pp\_args(p,i)] = \mathcal{T}(a_1) \to \cdots \to \mathcal{T}(a_m) \to \mathcal{T}(\frac{\lambda_{vt_1}}{\lambda_{vt_1}}) \to \mathcal{T}(\frac{\lambda_{vt_2}}{\lambda_{vt_2}}) \to \mathcal{T}(\frac{\lambda_{vt_2$$

for all  $a_i$  such that  $a_i \in alive(p,i)$  and for all  $vt_i$  such that  $vt_i \in inspect(p,i)$ .

The visit-function which performs the last traversal of a non-terminal does not return any partial parameterized visit-function. Its signature is:

$$\frac{\mathbf{\lambda_{p^n}} :: \mathsf{i} type\_pp\_args(p,i) \mathsf{;} \quad \mathcal{T}(inh\_1) \to \cdots \to \mathcal{T}(inh\_k) \to (\mathcal{T}(syn\_1), \ldots, \mathcal{T}(syn\_l))}$$

Let us now derive the code of the visit-function  $\lambda_{p^i}$ . It looks as follows:

$$\begin{array}{ll} \pmb{\lambda_{p^i}} & \textit{ipar\_par}(p,i)_{\dot{\mathcal{E}}} & \textit{jinherited}(i)_{\dot{\mathcal{E}}} = \\ & ((\pmb{\lambda_{p^{i+1}}} & \textit{ipar\_par}(p,i+1)_{\dot{\mathcal{E}}}), \textit{jsynthesized}(i)_{\dot{\mathcal{E}}}) \\ & \text{where } \textit{jbody}(i)_{\dot{\mathcal{E}}} \end{array}$$

and the visit-functions which performs the last traversal is:

```

\lambda_{p^n} [par_par(p, n) \dot{\varepsilon} [inherited(i) \dot{\varepsilon} = ([synthesized(i) \dot{\varepsilon})] where [body(n) \dot{\varepsilon}

```

where the code fragments defining the inherited and synthesized attributes look as follows:

$$jinherited(i)_{\dot{c}} = inh\_1 \ inh\_2 \dots inh\_k$$

$jsynthesized(i)_{\dot{c}} = syn\_1, syn\_2, \dots, inh\_k$

The code fragment  $par\_par(p, j)_{\dot{c}}$  denotes the partial parameterisation of the next visit-function.

$$ipar\_par(p,j)_{\dot{\mathcal{S}}} = a_1 \dots a_m \ \lambda_{vt_1} \dots \lambda_{vt_n}$$

The body  $jbody(i)_{\dot{\mathcal{E}}}$  of each visit-function  $\lambda_{p^i}$  is generated according to the instructions of the visit-sub-sequence vss(p,i). Every attribute equation of the form

$$\begin{array}{c} \texttt{eval}\;(p_q.a) \\ \texttt{uses}(attroccs) \end{array}$$

defining an attribute occurrence  $p_q.a = f(attroccs)$  of production p, generates an equation

$$(a_q) = f(attroccs)$$

Attribute  $p_r.a$  occurring in attroccs is replaced by  $a_r$ . Local attribute occurrences of productions are copied literally to the body of the respective visit-functions.

Every instruction visit(c, i) defining the visit i to non-terminal occurrence  $p_c$  introduces a call. Two cases have to be distinguished:

If  $i < v(p_c)$  then the call returns the partial parameterized function for the next traversal. The following equation is generated:

$$(\lambda_{p_c^{i+1}}, syn\_1_c, \dots, syn\_j_c) = \lambda_{p_c^i} inh\_1_c \dots inh\_l_c$$

If  $i = v(p_c)$  then only the synthesized attributes are computed by the function call.

$$(syn\_1_c, \dots, syn\_j_c) = \lambda_{p_c^i} inh\_1_c \dots inh\_l_c$$

with

$$\{inh_1, ..., inh_j\} = A_{inh}(p_c, i)$$

and  $\{syn_1, ..., syn_j\} = A_{syn}(p_c, i)$ .

Let us return to the BLOCK AG and derive the visit-function for the most intricate production: the production BLOCK. First we compute the set *alive* and the visit-trees for each visit to that production.

$$\begin{array}{ll} alive(\texttt{Block},1) &= \{ \ \} \\ alive(\texttt{Block},2) &= \{ \ lev_2 \ \} \\ inspect(\texttt{Block},1) &= \{ \ Its^1 \ \} \\ inspect(\texttt{Block},2) &= \{ \ Its^1 \ \} \end{array}$$

As expected, the attribute occurrence *It.lev* must be passed from the first to the second traversal. The two visit-functions derived for this production are:

```

\lambda_{Block1} ipar\_par(BLOCK, 1); lev_1 dcli_1 = ((\lambda_{Block2} \ ipar\_par(BLOCK, 2);, dclo_1) where ibody(1);

```

```

\lambda_{Block^2} ipar\_par(BLOCK, 2) \dot{c} env_1 = (errors_1) where ibody(2) \dot{c}

```

where the fragments  $ipar\_par\dot{z}$  are:

```

ipar\_par(BLOCK, 1)_{\dot{o}} = \lambda_{Its^1}

ipar\_par(BLOCK, 2)_{\dot{o}} = lev_2 \lambda_{Its^1}

```

The body of the visit-functions is trivially derived from the corresponding visit-sub-sequences (see figure 2): we present only the body of the visit-function for the second traversal to the production BLOCK.

```

jbody(2)\dot{g} = dcli_2 = env_1

(\lambda_{Its^2}, dclo_2) = \lambda_{Its^1} \ dcli_2 \ lev_2

errors_2 = \lambda_{Its^2} \ dclo_2

errors_1 = errors_2

```

The complete  $\lambda$ -attribute evaluator derived from the BLOCK attribute grammar is presented in figure 3 (some copy rules were trivially removed from the AE code).

```

\lambda_{Block^1} \lambda_{Its^1} dcli\ lev =

((\lambda_{Block^2}\ lev_2\ \lambda_{Its^1}), dcli)

\lambda_{RootP^1} \ \lambda_{Its^1} = errors_2

where lev_2 = lev + 1

where lev_2 = 1

dcli_2 = []

\lambda_{Decl^1} name deli lev =

(\lambda_{Its^2}, dclo_2) = \lambda_{Its^1} \ dcli_2 \ lev_2

(N_{Decl^2}! errors), dclo)

errors_2 = \lambda_{Its^2} \ dclo_2

where

dclo = (!name, lev) : dcli

errors = (name, lev)

\lambda_{ConsIts^1} \lambda_{It^1} \lambda_{Its^1_2} dcli \ lev =

'mustnotbein' deli

((\lambda_{ConsIts^2} \ \lambda_{It^2} \ \lambda_{Its^2}), dclo_3)

where (\lambda_{It^2}, dclo_2) = \lambda_{It^1} \ dcl\tilde{i} \ lev

\lambda_{Use^1} name dcli lev =

(\lambda_{Its_2^2}, dclo_3) = \lambda_{Its_2^1} dclo_2 lev

((\lambda_{Use^2} name), dcli)

\lambda_{NilIts^1} \ dcli \ lev = ((\lambda_{NilIts^2}), dcli)

\lambda_{Block^2} lev_2 \lambda_{Its^1} env = errors_2

\lambda_{ConsIts^2} \ \lambda_{It^2} \ \lambda_{Its_2^2} \ env = errors

where (\lambda_{Its^2}, dclo_2) = \lambda_{Its^1} env lev_2

where errors_2 = \lambda_{It^2} env

errors_2 = \lambda_{Its^2} \ dclo_2

errors_3 = \lambda_{Its_2^2} env

errors = errors_2 ++ errors_3

\lambda_{Decl^2} \ errors \ env = errors

\lambda_{NilIts^2} env = []

\lambda_{Use^2} name env = errors

where errors = name 'mustbein' env

```

Fig. 3. The complete  $\lambda$ -attribute evaluator for the BLOCK Language.

As a result of our techniques all visit-functions have become combinators, *i.e.*, they do not refer to global variables. The type of the  $\lambda$ -attribute evaluator is the type of the visit-function of the root symbol:

$$\lambda_{RootP^1} :: ([a] \rightarrow Int \rightarrow ([a] \rightarrow b, [a])) \rightarrow b$$

This evaluator returns the attribute errors (type b) and it has one function as argument: the visit-function which performs the first visit to the non-terminal symbol Its. This function has the initial environment (type [a]) and the level (type Int) as arguments and it returns a pair: the function for the second visit to Its (with type  $[a] \rightarrow b$ ) and the total environment.

As a result of generating HASKELL code we inherit many useful properties of this language. The  $\lambda$ -attribute evaluator of figure 3, for example, is completely polymorphic. In this evaluator nothing is defined about the type of the identifiers of the language. The identifiers are provided by an external lexical analyser. They can be a sequence of characters, a single character or even a numeral. The AE can be reused in all those cases, provided that the semantic functions must bein and must not bein are defined on that type too.

This approach has the following properties:

- The  $\lambda$ -attribute evaluators have the tendency to be more polymorphic.

- The evaluators are data type independent and, thus, new semantics can be easily added: for example, new productions can be incorporated to a compiler without having to change the evaluator. This property will be explained in section 4.

- Attribute instances needed in different traversals of the evaluator are passed between traversals as results/arguments of partial parameterized visitfunctions. No additional data structure is required to handle them, like trees [Kas91,PSV92,SKS97] or stacks and queues [AS91].

- The resulting evaluators are higher-order attribute evaluators. The arguments of the evaluators visit-functions are other AE visit-functions.

- The visit-functions find all the values they need in their arguments.

- No pattern matching is needed to detect the production applied at the node the evaluator is visiting.

- The visit-functions are strict in all their arguments, as a result of the order computed by the AG ordered scheduling algorithm.

- Efficient memory usage: data not needed is no longer referenced. References

to grammar symbols and attribute instances can efficiently be discarded as

soon as they have played their semantic role.

- The code of the attribute evaluator is shorter because no data structures are defined.

## 4 Parse-Time Attribute Evaluation

Traditional attribute grammar systems construct an abstract syntax tree during the parsing of the source text. This tree is used later to guide the attribute evaluator. For some classes of attribute grammars the construction of the abstract syntax tree may be avoided and the attribute evaluation may be performed in conjunction with the parsing (L-attributed grammars). In this case, it is the parser which guides the attribute evaluation. Such a model has several advantages, namely speed and space requirements. Methods exist which make one-pass attribute evaluation during parsing possible [ASU86].

Parse-time attribute evaluation is achieved as a by-product of our AG implementation: the parser directly calls the visit-functions which perform the first traversal of the  $\lambda$ -attribute evaluator.

Consider again the production Block. The classic fragment of the parser derived from the AG which defines this production and constructs the corresponding tree node looks as follows<sup>2</sup>:

```

It: blk '('Its')' \{ BLOCK $3 \}

```

The type of the parser derived from this specification is a function from a string (*i.e.*, the source text) to the type of the term defined by the production.

```

parser\_It :: [Char] \rightarrow It

```

where *It* is a declared data type.

Using our techniques the parser derived from the AG generates a call to the attribute evaluator visit-functions which perform its first traversal. Our parser looks as follows:

```

It: 	exttt{blk '('} Its')' \ \left\{ \begin{array}{l} \lambda_{Block^1} & \$3 \end{array}

ight\}

```

The deforestated visit-functions are partially parameterized with the arguments available at parse-time. Those arguments are the other visit-functions which are partially parameterized when parsing the grammar symbols of right-hand side of the production. No explicit abstract syntax tree is constructed.

Consider the visit-function  $\lambda_{NilIts^1}$  which returns the visit-function  $\lambda_{NilIts^2}$ . The function  $\lambda_{NilIts^2}$  is a constant function: it does not depends on its arguments. That is, it does not use the inherited attribute env and always returns an empty list (i.e., it evaluates the synthesized attribute errors). As result,  $\lambda_{NilIts^2}$  can be computed at parse-time.

Generally, every visit-function, derived from a visit-sub-sequence i which does not have inherited attributes (annotation inh) or which does not use its inherited attributes, can be evaluated in visit i-1. It has all the arguments it needs available on the previous visit. Observe that the visit-functions derived for productions applied to non-terminal symbols which only have synthesized attributes can be evaluated at parse-time. This is particularly important when implementing processors that produce code as the the input is being processed, i.e., for implementing online algorithms.

<sup>&</sup>lt;sup>2</sup> We use HAPPY [Mar97] notation, an Yacc equivalent for Haskell.

Suppose that we want to extend the Block language with named blocks. That is, the Block AG is extended with the following production:

```

It \rightarrow \text{NAMEDBLK} ('blk' name':','('Its')')

```

In traditional AG implementations, the attribute evaluator would have to be modified, since the type of the abstract syntax tree changes. Our implementation, however, is independent of the abstract tree data type. The attribute evaluator of figure 3 can be reused, without any modification, to implement the AG extension. The only part of the compiler that has to be modified is the parser: the new production must be included, obviously. Furthermore the visit-functions  $\lambda_{NamedBlk^i}$  which implement the different visits to the production have to be added to the compiler as a separate module. The new parser fragment looks as follows:

```

It: 	exttt{blk name ':' '(' } Its')' \ \left\{ \begin{array}{l} \lambda_{NamedBlk^1} & \$2 & \$5 \end{array}

ight\}

```

The signature of the visit-functions  $\lambda_{NamedBlk^i}$  must follow the partitions of the non-terminal symbol It (i.e., the symbol on the left-hand side of the production).

This property of our AG implementation is particularly important when designing language processors, in a component based style: AG components and the respective evaluators can be easily reused and updated, even when separate analysis and compilation of such components is considered [Sar].

## 5 Applications

This section describes how our techniques are used in the context of *Higher-Order Attribute Grammars*, *Incremental Attribute Evaluation*, *Composition of Attribute Grammars* and *Lazy Attribute Evaluation*.

Higher-Order Attribute Grammars (HAG) [VSK89]: the techniques described in this paper were developed in the context of the (incremental) evaluation of HAGs. HAGs are an important extension to the classical AG formalism: attribute grammars are augmented with higher-order attributes. Higher-order attributes are attributes whose value is a tree with which we associate attributes again. Attributes of these so-called higher-order trees, may be higher-order attributes again. Higher-order attribute grammars have two main characteristics: first, when a computation can not easily be expressed in terms of the inductive structure of a tree, a better suited structure can be computed first, and secondly, every computation (i.e., inductive semantic function) can be modeled through attribute evaluation. Typical examples of the use of higher-order attributes are mapping a concrete syntax tree into an abstract one and modelling symbol table lookups.

A higher-order attribute grammar may have several higher-order attributes (i.e., higher-order trees). Thus, an attribute evaluator for HAG may contain

a possibly large number of higher-order trees. As a result the efficiency of the attribute evaluator may be affected by the construction and destruction of those trees. The technique described in this paper can be used to implement higher-order attribute grammars [Sar]. The higher-order attributes are represented by their initial visit-functions.

Incremental Attribute Evaluation: one of the key features of our AG implementation is that the attribute evaluators are constructed as a set of strict functions. Consequently, an incremental attribute evaluator can be obtained through standard function caching techniques [PSV92]. The incremental behaviour is achieved by storing in a cache calls to the attribute evaluator functions and by reusing their results when such functions are later applied to the same arguments. This is the most efficient and elegant approach for the incremental evaluation of HAGs [Pen94,CP96]. Previous techniques, however, rely on additional data structures, e.g., a binding tree, to handle attribute instances needed in different traversals of the evaluator [Pen94]. A large number of calls to tree constructor functions may have to be cached since the number of binding trees is quadratic in the number of traversals. Such an approach, albeit optimal in the number of reevaluations, can result in a substantial decrease of performance of the incremental evaluator due to the fast growth, and consequent overhead, of the cache [SKS96]. Using  $\lambda$ -attribute evaluators no constructor functions exist (i.e., abstract tree nor binding tree constructor functions) and thus no constructor functions have to be cached! The calls to the visit-functions are the only calls actually cached. The incremental evaluators have less cache overhead [Sar].

Composition of Attribute Grammars: consider a compiler organized as follows: it has two AGs of the form  $ag_1 :: T_1 \to T_2$  and  $ag_2 :: T_2 \to T_3$ . That is, it has two AGs which are *glued* by the intermediate tree  $T_2$ . Using traditional AG techniques the tree  $T_2$  would have to be constructed. Using our techniques the attribute evaluator of  $ag_1$  directly calls the deforestated visit-functions of the  $ag_2$  attribute evaluator, like in a *normal* multiple traversal AE. As result, no intermediate tree is constructed. This strategy holds even when separate analysis (compilation) of both AGs is considered. In [Sar] this composition of attribute grammar components is presented.

Lazy Attribute Evaluation: attribute grammars can be easily and elegantly implemented in a programming language with lazy semantics [KS87,Joh87,SA98]. The techniques described here are orthogonal to the lazy mapping of attribute grammars. See [Sar] for the formal derivation of deforestated and lazily implementation of attribute grammars.

## 6 Implementation

The techniques described in this paper have been implemented in the LRC system [KS98], a purely functional attribute grammar system. The LRC processes Higher-Order Attribute Grammars, written in a super-set of Ssl, the *synthesizer*

specification language [RT89], and produces purely functional attribute evaluators.

We have developed a new back-end to the LRC in order to generate HASKELL based attribute evaluators. A (coloured) LATEX version of such attribute evaluators is also generated by the LRC system. Actually the HASKELL code presented in this paper (including the AE of figure 3) was automatically produced by LRC from a SSL specification. The deforestation of HAGs and the lazy implementation of attribute grammars, discussed in section 5, have also been implemented.

Several small and medium size  $\lambda$ -attribute evaluators have been translated into C in order to use the caching mechanism of the LRC system and to achieve incremental evaluation. The automatic generation of  $\lambda$ -attribute evaluators in the C language is currently being incorporated to LRC.

#### 7 Conclusions

This paper introduced a new technique for compiler construction. The compilers are constructed as a set of strict and purely functional visit-functions. All explicit data structure definition, construction and traversals have been removed. As a result of our technique the  $\lambda$ -attribute evaluators are totally generic and can easily be reused and updated across different applications. Because constructor funtions are never used, and all case statements have been "compiled way", one might in general expect better performance, since the flow of information is now clearly represented in the structure of the paremeters and results of the visit-functions. Thus, many compiler optimization techniques become enabled. Furthermore parse-time attribute evaluation is achieved as a by-product: the parser directly calls the visit-functions.

A simple language was analysed and the respective compiler was automatically derived from an attribute grammar. A mapping from attribute grammars into strict and purely functional attribute evaluator was defined. This mapping has been implemented in the LRC system.

The technique described in this paper is not restricted to the context of compiler construction only. It can be used to efficiently implement any algorithm which performs multiple traversals over a recursive data structure. It was used, for example, to implement a pretty printing combinator library [SAS98], which is a four traversal algorithm and that would have been extremely complicated to construct by hand.

## References

- AS91. Rieks Akker and Erik Sluiman. Storage Allocation for Attribute Evaluators using Stacks and Queues. In H. Alblas and B. Melichar, editors, *International Summer School on Attribute Grammars, Applications and Systems*, volume 545 of *LNCS*, pages 140–150. Springer-Verlag, 1991. 11

- ASU86. Alfred V. Aho, Ravi Sethi, and Jeffrey D. Ullman. Compilers: Principles, Techniques and Tools. Addison Wesley, 1986. 12

- CP96. Alan Carle and Lori Pollock. On the optimality of change propagation for incremental evaluation of hierarchical attribute grammars. ACM Transactions on Programming Languages and Systems, 18(1):16–29, January 1996. 14

- Joh87. Thomas Johnsson. Attribute grammars as a functional programming paradigm. In G. Kahn, editor, Functional Programming Languages and Computer Architecture, volume 274 of LNCS, pages 154–173. Springer-Verlag, September 1987. 14

- Kas<br/>80. Uwe Kastens. Ordered attribute grammars. Acta Informatica, 13:229–256,<br/>1980. 2, 4

- Kas91. Uwe Kastens. Implementation of Visit-Oriented Attribute Evaluators. In H. Alblas and B. Melichar, editors, *International Summer School on Attribute Grammars*, *Applications and Systems*, volume 545 of *LNCS*, pages 114–139. Springer-Verlag, 1991. 4, 11

- Knu<br/>68. Donald E. Knuth. Semantics of context-free languages. Mathematical Systems Theory, 2(2):127–145, June 1968.<br/>  ${\color{gray}2}$

- KS87. Matthijs Kuiper and Doaitse Swierstra. Using attribute grammars to derive efficient functional programs. In Computing Science in the Netherlands CSN'87, November 1987. 14

- KS98. Matthijs Kuiper and João Saraiva. Lrc A Generator for Incremental Language-Oriented Tools. In Kay Koskimies, editor, 7th International Conference on Compiler Construction, volume 1383 of LNCS, pages 298–301. Springer-Verlag, April 1998. 14

- Mar97. Simon Marlow. Happy User Guide. Glasgow University, December 1997. 12

- Pen94. Maarten Pennings. Generating Incremental Evaluators. PhD thesis, Department of Computer Science, Utrecht University, The Netherlands, November 1994. ftp://ftp.cs.ruu.nl/pub/RUU/CS/phdtheses/Pennings/. 4, 14

- PSV92. Maarten Pennings, Doaitse Swierstra, and Harald Vogt. Using cached functions and constructors for incremental attribute evaluation. In M. Bruynooghe and M. Wirsing, editors, *Programming Language Implementation and Logic Programming*, volume 631 of *LNCS*, pages 130–144. Springer-Verlag, 1992. 2, 11, 14

- RT89. T. Reps and T. Teitelbaum. The Synthesizer Generator. Springer, 1989. 15

- SA98. S. Doaitse Swierstra and Pablo Azero. Attribute Grammars in a Functional Style. In Systems Implementation 2000, Berlin, 1998. Chapman & Hall. 14

- Sar. João Saraiva. Purely Functional Implementation of Attribute Grammars. PhD thesis, Department of Computer Science, Utrecht University, The Netherlands. (In preparation). 13, 14

- SAS98. Doaitse Swierstra, Pablo Azero, and João Saraiva. Designing and Implementing Combinator Languages. In *Third International Summer School on Advanced Functional Programming, Braga, Portugal*, 1998. 15

- SKS96. João Saraiva, Matthijs Kuiper, and Doaitse Swierstra. Effective Function Cache Management for Incremental Attribute Evaluation. Technical report UU-CS-1996-50, Department of Computer Science, Utrecht University, November 1996. 14

- SKS97. João Saraiva, Matthijs Kuiper, and Doaitse Swierstra. Specializing Trees for Efficient Functional Decoration. In Michael Leuschel, editor, *ILPS97 Workshop on Specialization of Declarative Programs and its Applications*, pages 63–72, October 1997. (Also available as Technical Report CW 255, Department of Computer Science, Katholieke Universiteit Leuven, Belgium). 11

VSK89. Harald Vogt, Doaitse Swierstra, and Matthijs Kuiper. Higher order attribute grammars. In ACM SIGPLAN '89 Conference on Programming Language Design and Implementation, volume 24, pages 131–145. ACM, July 1989. 13

## Debugging Eli-Generated Compilers with Noosa

Anthony M. Sloane

Department of Computing, Macquarie University Sydney, NSW 2109 Australia asloane@mpce.mq.edu.au

Abstract. Source-level tools are not adequate for debugging generated compilers because they operate at the level of the generated implementation. It is inappropriate to expect compiler writers to be familiar with the implementation techniques used by the generation system. A higher-level approach presents debugging in terms of an abstract model of the implementation. For example, finite-state machines might be shown while debugging a scanner. This approach is inappropriate for developers who are not compiler experts and even for experts may present more information than is desirable.

An even higher-level approach is used by the Noosa graphical debugger for the Eli compiler generation system. The compiler writer is required to understand a simple execution model that involves concepts that they already have to understand to write Eli specifications. Noosa allows highlevel data examination in terms of the input to the compiler and the abstract trees upon which attribution is performed. An event system allows fine-tuned control of program execution. The result is a debugging system that enables developers to diagnose bugs without having to have any knowledge of the underlying mechanisms used by their compiler.

## 1 Introduction

A variety of methods have been developed for automatically producing compilers from specifications. Using these techniques, a compiler writer can write a high-level specification of compiler functionality and a generation system will produce an implementation that conforms to that specification. Compiler generation has been successful mainly due to the existence of a range of specification notations covering important sub-problems, and the development of efficient methods for implementing these notations (for example, see [4,9,12,14,19]).

The major advantage of generation systems is that they enable a compiler writer to concentrate on the important issues while the responsibility for producing a correct implementation rests with the system. A generation system that is functioning correctly is no guarantee of a correct compiler, however, because the specification may have bugs.

Compiler generation systems typically provide very little in the way of debugging facilities. Source-level debuggers such as Dbx [8] or GDB [16] can be applied to generated compiler implementations, but this approach is largely unsatisfactory because it requires compiler writers to have specific knowledge about

the implementation methods used by the generator. Requiring such knowledge defeats the main purpose of a generation system.

This paper describes the Noosa debugger for programs generated by the Eli compiler generation system. Eli generates compilers using a collection of specification notations including regular expressions for token description, context-free grammars for concrete and abstract syntax, and attribute grammars for semantic analysis and later phases.

Noosa presents a graphical view of the execution of a generated compiler in terms of the input being processed by it. The compiler writer can examine how their regular expressions and grammar productions were used to structure the input. Access is also provided to major compiler data structures such as the abstract trees upon which attribution takes place, environment structures and the definition table. Attribute values of any tree node can be examined in a flexible browsing system that is easily extended to new data types. The developer also has access to an abstract event stream produced by the running compiler. User-specified event handlers can be written in the Tcl language. This facility enables the specification of complex debugging operations such as semantic breakpoints and correlation of information from disparate sources.

The goal of Noosa is to provide debugging facilities that operate at the specification level, hiding the implementation details as much as possible. The aim is to achieve a level of implementation-hiding similar to source-level debuggers operating on programs compiled to machine language. In those debuggers the developer is able to interact with their program's execution in terms with which they are familiar. For example, data can be accessed via variable names and the control state is presented in terms of a stack of active routines and the statement about to be executed. Knowledge of all of these aspects can be expected of any programmer familiar with the source language.

Noosa does not present details of the implementation of compiler components. According to this philosophy, if the specification of the compiler includes regular expressions to describe token types then it is appropriate to present information in terms of tokens, where they were located in the input, and the regular expressions that matched them. Detail about the functioning of the finite-state machine that implements the scanner is not suitable because it relies on knowledge that the compiler writer may not have. This approach contrasts with other debuggers for generated components that present a large amount of internal detail.

Noosa can also work in combination with source-level tools. Eli allows arbitrary C code to be included in the generated compiler to implement abstract data types or to code a part of the functionality that is hard to specify. To accommodate debugging of this code, Noosa can be used in conjunction with a source-level debugger. Thus specification-level and source-level debugging can be undertaken at the same time.

Section 2 considers the execution model that should form the basis of a debugger for generated compilers and describes the model used by Noosa. Section 3 describes the basic elements of the Noosa design with reference to the execution

model. Section 4 illustrates the Noosa style of debugging by describing typical compiler bugs and how Noosa would be used to diagnose them.

## 2 Execution Model

The functionality of a debugger is grounded in the facilities it provides for controlling execution of the program and the methods by which the program's state can be examined. For example, in most source-level debuggers breakpoints allow execution to be stopped when specific points in the code are reached. When execution is stopped, the values of program variables can be printed. Some debuggers have more advanced features such as conditional and data-dependent breakpoints or graphical displays of data structures, but the basic features are common to all source-level debuggers.

The kind of execution control and data access provided by a debugger depends intimately on an execution model that the debugger shares with its user. An execution model is a description of the structure of a program execution in terms of elementary actions and data items. An understanding of the program code and the execution model used by a debugger is necessary for the user to be able to operate debugger facilities and understand the output from debugging operations. For example, to use breakpoints in a debugger for an imperative language a user must understand the basic units of execution (e.g., statements) and the way execution proceeds (e.g., step-wise execution of statements plus routine calls). The state displayed by the debugger might also rely on the execution model (e.g., a stack of currently active routine calls).

Different debuggers for the same language can have different execution models that reflect the outcomes of design decisions about the kind of debugging that is to be permitted. For example, some source-level debuggers provide facilities for debugging at the machine level such as instruction stepping or the ability to examine the contents of registers. Other debuggers might omit such features on the grounds that machine level details are not relevant for a user of a high-level language. In general, the execution model to be used by a debugger depends on the view of execution that the debugger is trying to present.

In the compiler generation domain there are choices of execution model. If a source-level debugger is used to debug a generated compiler, the execution model is one appropriate to the implementation language. Even if the compiler writer is familiar with that language, they will in general not be experts in the generated code. Thus the use of an implementation language execution model is inappropriate.

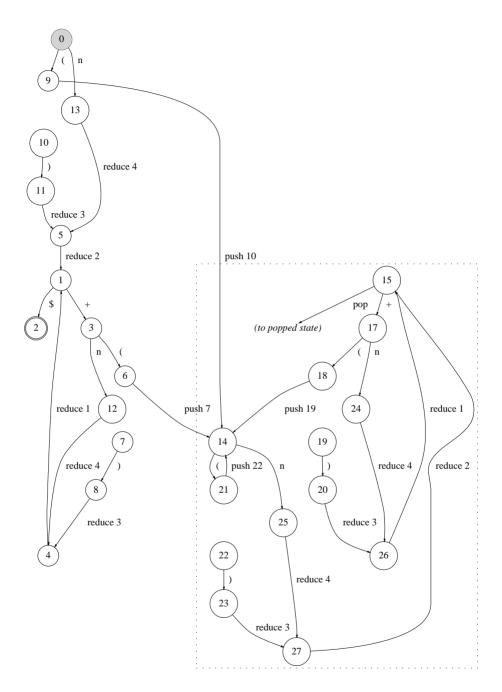

At a higher level of abstraction lies a class of execution models based on the methods used to implement compiler components. For example, a generated scanner might use a finite-state machine implementation. An execution model for a debugger operating at this level might include concepts such as finitemachine states, input characters, and legal state transitions. Execution could be presented in terms of the actual transitions performed during scanning, perhaps with a visual representation of the machine. Some compiler tools offer tracing facilities at this level. For example, parsers generated by YACC [7] and derivatives like Bison [3], can produce a trace of the parsing process. The trace consists of events such as getting a token, shifting a symbol, reducing via a rule, and changing parser state.

More user-friendly alternatives at this level exist in the form of debuggers that present the same kind of information as a trace, but in a graphical, browsable form. For example, Visual Parse++ from SandStone Technology Inc. [6] presents the developer with an extremely detailed view of the operation of generated parsers. Information presented includes depictions of the parse stack, lookahead tokens and three-dimensional views of parse trees. The recently released ParseView debugger bundled with the latest version of the ANTLR tool [13] seems to offer similar features.

The design of Noosa follows a higher-level approach. The execution model used by Noosa does not include anything to do with the implementation of generated components. Of course, compiler writers may well need to know something about component implementations in order to use Eli. For example, writing an Eli grammar may require some knowledge of the LALR parsing method since both of Eli's parser generators use that method and the system will reject non-LALR(1) grammars. Similarly, using Eli's attribute grammar notations may require some knowledge of allowable patterns of attribute dependences and the methods used by generated evaluators. The philosophy behind Noosa is that knowledge of this kind is not needed during debugging.

Some anecdotal support for this position was obtained recently when Noosa was used by final year students in an introductory compiler unit at Macquarie University. The students were able to use Noosa to debug Eli specifications containing regular expressions and context-free grammars. In this unit the students are acquainted with the compilation phases and their purposes, but the implementation techniques used by the tools are only covered in outline form. Thus there is some evidence that such knowledge is not necessary for debugging.

Justification for the Noosa position as a goal can also be obtained from a recognition that the widespread availability of compiler generation systems has resulted in many non-compiler experts attempting to develop compilers (or compiler-like programs). For these users it is important that the debugging system not rely on knowledge that they do not have.

It should be noted that the more advanced features in the debuggers mentioned above are presumably at least partly inspired by the more complex specification notations and implementation methods used in those systems compared to Eli. For example, the ANTLR parsers use multiple symbol lookahead and more advanced debugger support may well be necessary for the user to understand what is happening. Whether this situation is an argument for more complex debuggers or less complex specification notations and implementation methods is unclear. In any event, Noosa operates within the environment provided by the Eli notations and methods.

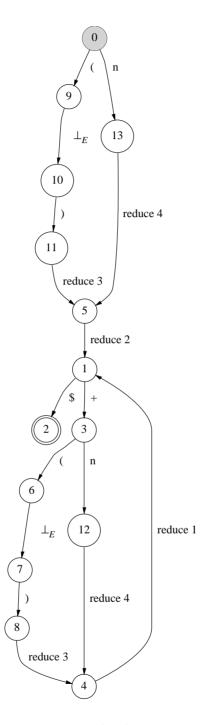

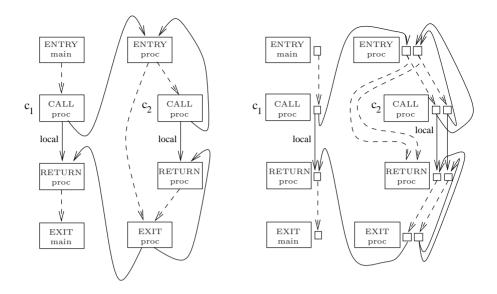

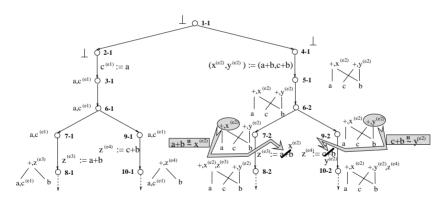

Figure 1 shows the execution model used by Noosa expressed in pseudocode. An Eli-generated program under the control of Noosa will scan the input attempting to locate tokens and trying to group those tokens into syntactic phrases. When a complete phrase is recognised an abstract tree fragment will be built to represent it and its components. Once the complete input has been recognised the tree is then decorated with attribute values. Usually a side-effect of one or more attribute evaluations will be to produce the compiler output. (To simplify the discussion we ignore the fact that attribution can occur during tree construction and that attribution can produce further trees which are in turn attributed. Both of these aspects are also supported by Noosa.)

```

\begin{array}{c} \underline{\textit{while}} \ \textit{there is more input } \underline{\textit{do}} \\ \\ \underline{\textit{get the next token}} \\ \underline{\textit{if}} \ \textit{a complete syntactic phrase has been recognised } \underline{\textit{then}} \\ \\ \underline{\textit{build an abstract tree fragment for the new phrase}} \\ \underline{\textit{while}} \ \textit{there are more tree attributes to evaluate } \underline{\textit{do}} \\ \\ \underline{\textit{perform an attribute evaluation}} \end{array}

```

Fig. 1. Noosa's execution model.

The concepts in the Noosa execution model are ones with which an Eli user can be expected to be familiar. The form of tokens is specified by the user using regular expressions or literals in the context-free grammar. The context-free grammar also specifies the valid phrases. The user's attribute grammar describes the abstract tree structure and the attribute computations that must be evaluated. These specification notations and their underlying concepts must be understood before a compiler can be specified using Eli.

#### 3 Noosa

Noosa's design is based on the execution model presented in the previous section. The input and the abstract tree play a central role in the user interface appropriate to their prominence in the model. Other data items can be accessed via a flexible browsing system designed to be easy to use and extensible to new data types. An event mechanism is used to allow both the debugger and the user to determine which actions are performed by the compiler being debugged and when they occur.

The rest of this section describes the main elements of the Noosa design. The discussion of features is structured according to the relevant elements of the execution model. Some mundane features such as menu invocations, searching in text windows, saving the context of text windows, file editing, on-line help, etc. are omitted. Example screenshots are taken from a debugging session for an Eli-generated C processor.

## 3.1 Input

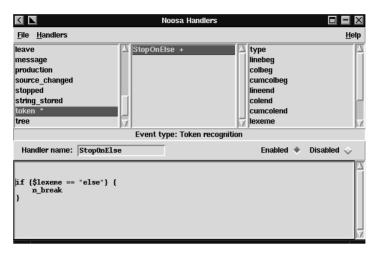

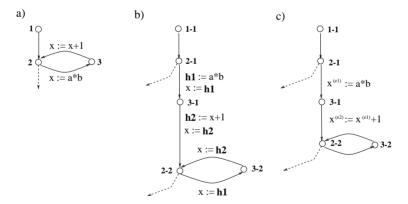

The starting point of a compilation is the input that is to be analysed and translated. Thus the main user interface of Noosa features the input (Figure 2).

**Fig. 2.** Main Noosa window. The upper text window shows the compiler input (a C word counting program). The lower text window is a transcript of debugging output showing the phrase structure at the equality operator in the highlighted if statement and the tokens in that if statement.

Noosa correctly accounts for input processing that obtains text from multiple sources. For example, if the language has an "include" facility and the compiler expands includes during parsing, the input text window will show the complete input seen by the compiler. This removes any need for the user to guess what

the compiler is working with or pre-process the input specially before debugging. The user can ask Noosa for the original source of any part of the input.

#### 3.2 Phrases and Tokens

Syntactic phrases and lexical tokens play a central role in the user's understanding of their compiler. Noosa enables the user to determine which phrases and tokens are recognised by the compiler. Each one is associated with a region of the input text. Thus Noosa's "Phrase" and "Token" commands are invoked relative to coordinates in the input text.

To see the phrases recognised at a particular location in the input the user selects the location with the mouse and invokes "Phrase." This action produces a list of the concrete grammar productions that have been recognised whose coordinate ranges overlap the indicated location. For example, the transcript (bottom text window) in Figure 2 shows productions involved in recognising the equality operator in the highlighted if statement. The productions are listed in order from the axiom of the grammar (not shown) to the most specific. The coordinate range beside each instance indicates the input recognised by that instance.

The coordinate display for phrases is an instance of a "browsable value" (indicated by the underline). Browsable values can be clicked to obtain behaviour dependent on the kind of value. Clicking on a coordinate or coordinate ranges causes the indicated input to be highlighted in the input text window. Thus it is easy to see the input corresponding to a particular recognised production instance.

The "Token" command operates in a similar fashion to "Phrase." To see the tokens scanned in a particular region the user selects the region in the input text window with the mouse and invokes "Token." The transcript lists the relevant tokens (if any). For example, the transcript in Figure 2 shows the tokens from the highlighted if statement. The coordinate range of each token is shown along with the token code, intrinsic value<sup>1</sup>, length and lexeme. Tokens which are non-literals and hence specified using regular expressions are also labelled with the regular expression name from the user's specification.

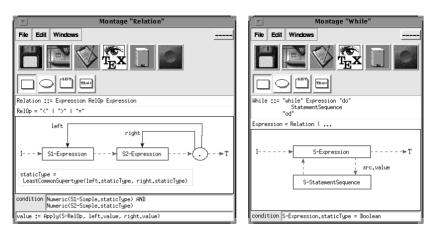

#### 3.3 Abstract Tree